The Verilog Hardware Interface for CAE

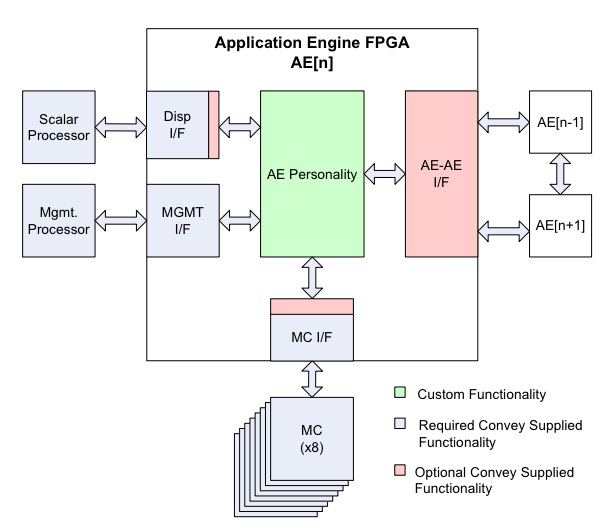

This article describes Convey's various hardware interfaces for use with a CAE (Custom Application Enginer). This should be useful when writing VHDL and developing your own bitfiles. When looking at the sample project, these interfaces can be found in the cae.v file.

Note: Each interface is between a component and your CAE. Inputs are signals sent to your CAE. Outputs are signals your CAE sends to the interface.

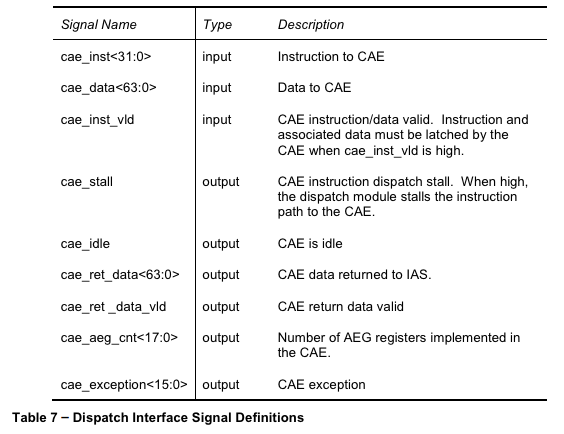

Dispatch Interface

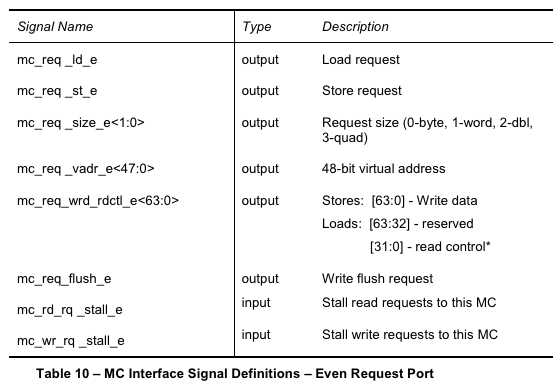

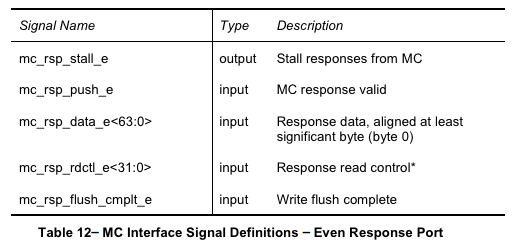

Memory Controller Interface

There are 8 memory controllers (MC). Each memory controller has two ports (even and odd). Even ports have signal names with a suffix of _e. Odd ports have a suffix of _o.

Request Port

Response Port

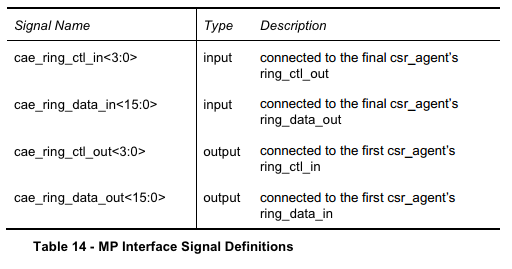

CSR Interface (Optional)

Simply connect the outputs and inputs together if you do not want to use any CSR agents.

References

- Convey PDK Reference Manual (.pdf) - Sections 9.3.2 - 9.3.?